# 「歐洲晶片法」簡介

駐歐盟經濟組提供 112.09.21

## 一、法案重點

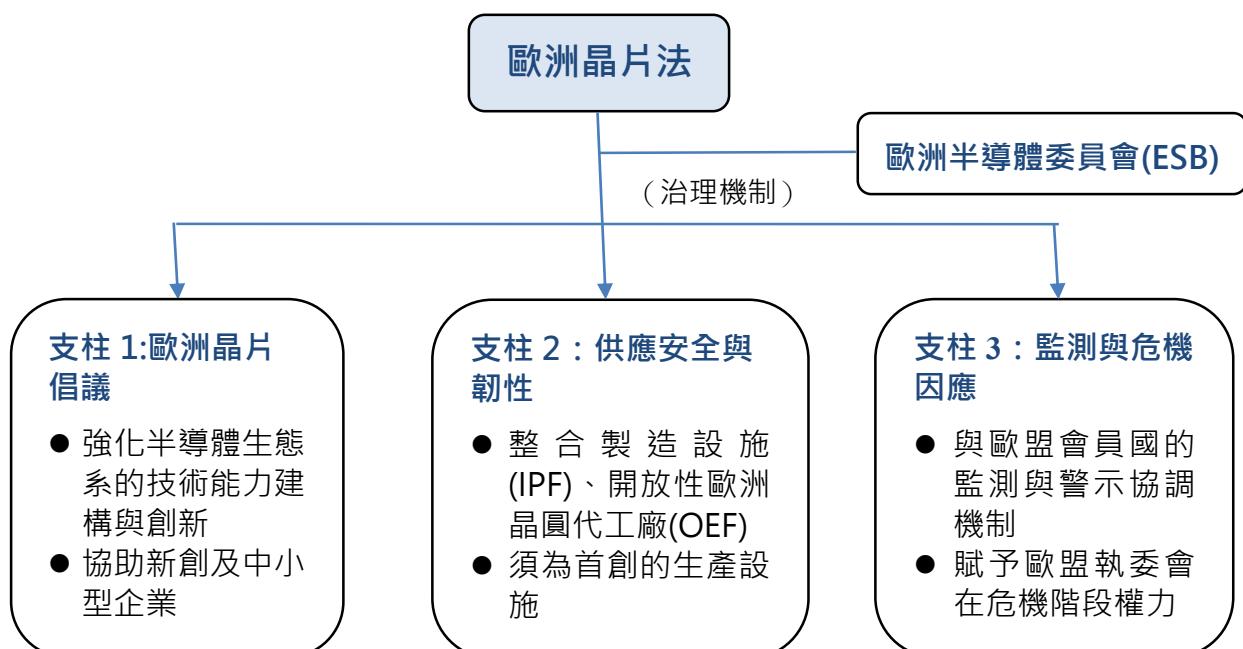

為增進歐盟半導體生態系韌性，及於 2030 年提高歐盟全球半導體市場佔有率至 20% 之戰略目標，歐盟執委會於 2022 年 2 月 8 日提出「歐洲晶片法」(EU Chips Act)<sup>1</sup>。該法案於 2023 年 9 月 13 日由歐洲議會及歐盟部長理事會簽署，同年 9 月 18 日公告，公告後第 3 日生效。該法案分為 8 章節、41 條條文，主係基於三大支柱架構，重點如次：

### (一) 支柱 1：歐洲晶片倡議(Chips for Europe Initiative)

該倡議經費將分別由展望歐洲(Horizon Europe)支應 17.25 億歐元(研究與創新活動)及數位歐洲計畫(Digital Europe Programme)支應 15.75 億歐元(能力建構活動)，共計 33 億歐元，以支持整個歐盟的大規模技術能力建構與創新；並透過歐盟「晶片聯合執行計畫」(Chips Joint Undertaking)強化歐洲半導體生態系「從實驗室到工廠」(from lab to fab)能力，包括：

1. 建立整合半導體技術之先進設計能力：將建立虛擬設計平台以整合現有設計機構及電子設計自動化(electronic design automation, EDA)工具；

2. 強化現有或新建試驗線(pilot lines)，以發展及部署尖端(cutting-edge)及下世代半導體技術(next-generation semiconductor technologies)；

3. 建立先進技術及工程能力以加速尖端量子晶片(quantum chips)及相關半導體技術的創新發展；

4. 建立能力中心網絡(a network of competence centres)：為產業提

---

<sup>1</sup> COM(2022) 45 final

供專業知識，解決人力短缺、吸引人才等功能；

5. 透過**晶片基金**(Chips Fund)活動以加速獲取債務融資及股權：透過InvestEU 等機制，為半導體價值鏈之新創、中小企業等提供資金。

## (二) **支柱 2：供應安全與韌性(Security of supply and resilience)**

透過吸引投資及提高生產能力，以改善歐盟的半導體供應安全，並擬訂相關計畫可申獲歐盟國家補助之標準及審核要素：

1. 主要分為「**整合製造設施**」(Integrated Production Facilities, **IPF**)，及「**開放性歐洲晶圓代工廠**」(Open EU Foundries, **OEF**) 兩大類，須符合以下標準：

- (1) 為「**首創設施**」(first-of-a-kind facility)<sup>2</sup>；

- (2) 其建置與營運對歐盟半導體中長期價值鏈，在確保供應安全及半導體生態系韌性，包括新創與中小企業成長及對歐盟綠色與數位轉型等方面，具明確正面影響；

- (3) 保證不受**第三國政府**域外適用拘束；

- (4) 其投資將持續創新以達成半導體技術之具體進展或為下世代技術準備；

- (5) 透過開發與部署教育與技能訓練及增加技術勞動以支持**歐盟人才儲備**。

2. 半導體業者倘擬於歐盟地區投資設廠，得向歐盟執委會申請認定為IPF 或 OEF 設施。在審核要素方面，除評估是否符合上述標準外，尚包括其財務與技術可行性、裝置與營運經驗、設施所在地會員國已準備好促進相關建設的證明文件，以及是否有適當的政策如技術保護與執行措施等。歐盟執委會需在接受完備申請 6 個月內通知申

---

<sup>2</sup> first-of-a-kind facility' means a new or substantially upgraded semiconductor manufacturing facility, or a facility for the production of equipment or key components for such equipment predominantly used in semiconductor manufacturing, which provides innovation with regard to the manufacturing process or final product that is not yet substantively present or committed to be built within the Union, including innovation that concerns improvements in computing power or in the level of security, safety or reliability, energy and environmental performance, the technology node or substrate materials, or in the implementation of production processes that lead to efficiency gains, or improves recyclability, or reduces production inputs .

請者其決定。

3. 歐盟執委會針對境內透過提供服務或發展、促進與強化設計技能，以顯著提升歐盟創新晶片設計能力的設計中心，可授予「**卓越設計中心(design centre for excellence)**」標章。歐盟會員國可根據現有立法，對獲得此標章之設計中心給予支持措施。

4. 歐盟會員國得對 IPF 或 OEF 提供補助等優惠措施及行政支援，對相關計畫、建造與營運之申請，得視為符合公共利益及具最高國家重要性，爰應確保在許可程序方面以**快軌(fast-tracking)**方式處理。IPF 及 OEF 在符合前所稱持續創新的投資目的下，可優先使用試驗線設施。

### **(三) 支柱 3：監測與危機因應(Monitoring and crisis response)**

旨在建立歐盟執委會與會員國之間在監測與危機因應協調機制。

1. 歐盟執委會需與新成立之「歐洲半導體委員會」(European Semiconductor Board, ESB)合作制定**歐盟半導體產業策略性地圖(strategic mapping)**，以分析歐盟在全球半導體產業的優劣勢及重要影響因素包括關鍵產品、主要使用產業、供應鏈關鍵環節、技術特性及技能需求等。

2. 歐盟執委會依據前述之策略性地圖結果，經諮詢 ESB 後，應制定「**早期預警指標**」(early warning indicators)，由歐盟會員國據以進行監測，依境內關鍵業者所提供之資訊，監視半導體貨品與服務之可用性，並定期提交歐洲半導體委員會。

3. 歐盟會員國倘認為有潛在半導體供應危機，應向歐盟執委會示警，以召開 ESB 會議評估是否啟動「**危機階段**」(crisis stage)，並採取緊急應變行動，包括：歐盟執委會可要求個別企業提供生產能量資訊，及要求 IPF 與 OEF 接受「**優先級別訂單**」(priority-rated orders)，

或進行**共同採購**(common purchasing)、與第三國協商合作等，以緩解半導體供應短缺與干擾問題。

4. 歐盟執委會經與 ESB 諮商後，可向歐盟部長理事會提案啟動危機階段，部長理事會採多數決通過後可啟動危機階段，惟期間不超過 12 個月。

(四) **治理機制**：歐盟半導體委員會(ESB)應由所有會員國代表組成，並由歐盟執委會的代表擔任主席。ESB 應提供歐盟執委會對於本法之意見、協助與建議，同時確保在危機因應與整備的協調、合作和資訊交流。

圖 1: 歐洲晶片法架構